# Exploiting Deferred Destruction: An Analysis of Read-Copy-Update Techniques in Operating System Kernels

Paul E. McKenney

B.S., Mechanical Engineering, Oregon State University, 1981

B.S., Computer Science, Oregon State University, 1981

M.S., Computer Science, Oregon State University, 1988

A dissertation submitted to the faculty of the OGI School of Science & Engineering at Oregon Health & Science University in partial fulfillment of the requirements for the degree Doctor of Philosophy

1n

Computer Science and Engineering

July 2004

© Copyright 2004 by Paul E. McKenney All Rights Reserved The dissertation "Exploiting Deferred Destruction: An Analysis of Read-Copy-Update Techniques in Operating System Kernels" by Paul E. McKenney has been examined and approved by the following Examination Committee:

Jonathan Walpole Professor Thesis Research Adviser

Andrew Black Professor

Mark P. Jones Associate Professor

Orran Krieger IBM Research Adjunct Professor U. of Toronto Carnegie-Mellon U.

Michael Scott Professor University of Rochester

# Dedication

To my wife, Gloria Wyffels, and to our children, Melissa, Sarah, and Aaron.

# Acknowledgements

I am indebted to both Jack Slingwine, co-inventor of RCU whose implementation within ptx/CLUSTERS was the first to ship to DYNIX/ptx customers, and to Dipankar Sarma, who did much of the hard work that lead to RCU's widespread use within the Linux 2.6 kernel, for extremely exciting and productive collaborations.

I am grateful to to Dave Stewart, Robin O'Neill, and Mike Paschal, who were willing to stake their respective products' release dates and reputations on RCU. Given that less than a year prior, RCU had been but a topic of discussion, this willingness bespeaks intestinal fortitude of mythic proportions.

I owe thanks to Stuart Friedberg, Doug Miller, Jan-Simon Pendry, Chandrasekhar Pularmarsetti, Peter Strazdins, and Dave Wolfe for their willingness to try out RCU, and to Ken Dove, to Brent Kingsbury, to Phil Krueger and his Base-OS Reading Group, and to my Bangalore students for many helpful discussions.

I am grateful to Wayne Cardoza, who very patiently explained the intricacies of the Alpha CPU's memory barriers, and similarly to Gary Oliver, who explained OS-3's use of the CDC 3300's interrupt system.

I am indebted to James Hennessy, Damian Osisek, and Joseph Seigh for discussions on the use of passive serialization in IBM's VM/XA product, to Luke Browning, Carl Burnett, Tom Mathews, and James Moody, for discussions on related topics in AIX, and to the K42 and Tornado groups, including Orran Krieger, Jonathan Appavoo, Marc Auslander, Dilma Da Silva, David Edelsohn, Michal Ostrowski, Bryan Rosenburg, Bob Wisniewski, and Jimi Xenidis, for excellent discussions and exchanges surrounding K42 generations, the combination of RCU and non-blocking synchronization, and alternative implementations of RCU infrastructure in Linux.

I am similarly indebted to a great number of Linux-community members. Dipankar Sarma implemented Linux's RCU infrastructure, and, together with Maneesh Soni, took on some of the less newbie-friendly portions of Linux. Andi Kleen, Rusty Russell, and Andrea Arcangeli each created alternative RCU-infrastructure implementations, using extremely clever and unexpected techniques. People participating in discussions, producing patches, trying out RCU, and otherwise keeping me honest include Al Dunsmuir, Al Viro, Alan Cox, Alexey Kuznetsov, Andrew Hutton, Andrew Morton, Andrew Tridgell, Andrey Panin, Anton Blanchard, Arnaldo Carvalho de Melo, Balbir Singh, Ben LaHaise, Benjamin Herrenschmidt, Bill Hartner, Bill Irwin, Brian Gerst, Christoph Hellwig, Cliff White, Corey Minyard, Daniel Phillips, Dave Hansen, Dave Jones, David Miller, Davide Libenzi, Don Marti, Ed Tomlinson, Erich Focht, Erik Anderson, Erlend Aasland, Fabian Frederick, George Anzinger, Gerrit Huizenga, Greg Kroah-Hartman, Hanna Linder, Hugh Blemings, Hugh Dickens, Ingo Molnar, Ivan Kokshaysky, J. W. Schultz, James Morris, Jamie Lokier, John Levon, Jonathan Corbet, Kai Henningsen, Karim Yaghmour, Keith Owens, Ken Rozendal, Kevin O'Connor, Luca Barbieri, Manfred Spraul, Marc-Christian Peterson, Mark Fasheh, Mark Hahn, Martin Bligh, Matt Dobson, Matt Mackall, Michael Baxter, Mikael Pettersson, Mingming Cao, Mitchell Blank Jr., Nikita Danilov, Oliver Neukum, Paul Mackerras, Pavel Machek, Peter Waechtler, Ravikiran Thirumalai, Richard Henderson, Rik Van Riel, Robert Love, Robert Olsson, Roman Zippel, Sam Ravnborg, Stephen Hemminger, Ted T'so, Thomas Schlichter, Trond Myklebust, Troy Wilson, Vamsi Krishna, Victor Yodaiken, Werner Almesberger, Zwane Mwaikambo, and Linus Torvalds. I learned at least as much about RCU in the past three years working with the Linux and K42 communities as I did in years prior.

I owe thanks to Bart Massey and Robert Bauer, who, much to my surprise, showed me that a formal definition of RCU semantics might well have practical applications.

I owe a debt of gratitude to my managers, Dale Goebel, Leslie Swanson, Rick Warren, Daniel Frye, Mark Dean, Chris Maher, Juergen Deicke, and Jai Menon, for their support of my work with RCU over more years than I care to count, and to my program committee, Jon Walpole, Andrew Black, Mark Jones, Orran Krieger, Michael Scott, for their inspiration and guidance.

This work was done with the aid of Macsyma, a large symbolic manipulation program developed at the MIT Laboratory for Computer Science and supported from 1975 to 1983 by the National Aeronautics and Space Administration under grant NSG 1323, by the Office of Naval Research under grant N00014-77-C-0641, by the U.S. Department of Energy under grant ET-78-C-02-4687, and by the U.S. Air Force under grant F49620-79-C-020, between 1982 and 1992 by Symbolics, Inc. of Burlington Mass., and since 1992 by Macsyma, Inc. of Arlington, Mass. Macsyma is a registered trademark of Macsyma, Inc. May it rest in peace.

Other portions of this work were done with the aid of Maxima, a large open-source symbolic manipulation program.

SPEC<sup>TM</sup> and the benchmark name SPECweb<sup>TM</sup> are registered trademarks of the Standard Performance Evaluation Corporation. The benchmarking was done for research purposes only and may not be compared to published results on the SPECWeb site, due to the following deviations from the rules:

- 1. It was run on hardware that does not meet the SPEC availability-to-the-public criteria. The machine was an engineering sample.

- 2. access\_log was not kept for full accounting. It was being written, but deleted every 200 seconds.

For the latest SPECweb99 benchmark results visit http://www.spec.org.

I owe thanks to OSDL for running many benchmarks used to evaluate RCU on Linux, and no dissertation is complete without an expression of thanks to Google.

I am grateful to Sequent Computer Systems, Inc. for providing the opportunity and hardware needed for the original development of RCU, as well as to IBM for continuing to provide such an environment, for their generous sharing of RCU with the Linux community, and for their wholehearted ongoing support of the Linux RCU effort.

Finally, I am indebted to Barry Leiner (in memoriam), Craig Partridge, Dale Goebel, Diane Lee, Lixia Zhang, and Phillip Kreuger for their help in getting me started down this road. After all, if you are not going to start a doctorate in the year 2000, when are you going to start on it?

# Contents

| D | edica          | tion   |                                                                         |

|---|----------------|--------|-------------------------------------------------------------------------|

| A | ckno           | wledge | ${f ments}$                                                             |

| A | bstra          | ict    |                                                                         |

| 1 | Intr           | oducti | on                                                                      |

|   | 1.1            | Where  | Has Moore's Law Gone Wrong?                                             |

|   | 1.2            | SMMF   | P Efficiency: The Effect on Real Code                                   |

|   | 1.3            | What   | Can Be Done?                                                            |

|   | 1.4            | Return | ning to Basic Principles                                                |

|   | 1.5            | Descri | $ ption of RCU \ldots \ldots \ldots \ldots                            $ |

|   | 1.6            | RCU I  | Research Challenges                                                     |

|   | 1.7            | Contri | butions of this Dissertation                                            |

| 2 | $\mathbf{Rel}$ | ated W | /ork                                                                    |

|   | 2.1            | Synchi | conization in Uniprocessor Systems                                      |

|   | 2.2            | Synchi | conization in SMMP Systems                                              |

|   |                | 2.2.1  | Spinlocks                                                               |

|   |                | 2.2.2  | SMMP Semaphores                                                         |

|   |                | 2.2.3  | Performance of SMMP Locking                                             |

|   |                | 2.2.4  | Hash-Table Mini-Benchmark                                               |

|   |                | 2.2.5  | Code Locking                                                            |

|   |                | 2.2.6  | Reader-Writer Locking                                                   |

|   |                | 2.2.7  | Partitioning and Data Locking                                           |

|   |                | 2.2.8  | Combining Data Locking and Reader-Writer Locking                        |

|   |                | 2.2.9  | Asymmetrical Reader-Writer Locking                                      |

|   |                | 2.2.10 | Read-Side Performance Analysis                                          |

|   |                | 2.2.11 | Write-Side Performance Experiment                                       |

|   |                | 2.2.12 | Operating-System Partitioning                                           |

|   |                | 2.2.13 | Simple Non-Blocking Synchronization                                     |

|   |     | 2.2.14 General Non-Blocking Synchronization              |

|---|-----|----------------------------------------------------------|

|   |     | 2.2.15 Transactional Hardware                            |

|   |     | 2.2.16 Exploiting Semantics                              |

|   |     | 2.2.17 Read-Mostly Linked-List Insertion                 |

|   |     | 2.2.18 Read-Mostly Linked-List Removal                   |

|   |     | 2.2.19 Read-Mostly Linked-List Removal and Reclaiming 59 |

|   |     | 2.2.20 Deferred Destruction                              |

|   | 2.3 | Discussion                                               |

|   |     | 2.3.1 Costs                                              |

|   |     | 2.3.2 Principles                                         |

|   |     | 2.3.3 Attributes                                         |

| 3 | DC1 | U Overview                                               |

| J | 3.1 | Introduction to RCU                                      |

|   | 3.2 | How RCU Solves Concurrency Problems                      |

|   | 0.2 | 3.2.1 Readers and Writers                                |

|   |     | 3.2.2 Multiple Versions                                  |

|   |     | 3.2.3 Writer-Writer Synchronization                      |

|   |     | 3.2.4 Reader-Writer Synchronization                      |

|   |     | 3.2.5 Weak Memory-Consistency Semantics                  |

|   | 3.3 | Conceptual Overview of RCU                               |

|   | 3.3 | 3.3.1 RCU Glossary                                       |

|   |     | 3.3.2 RCU Design Tradeoffs                               |

|   | 3.4 | Examples                                                 |

|   |     | 3.4.1 RCU Applied to Reader-Writer Locking               |

|   |     | 3.4.2 RCU Use of Deferred Destruction                    |

|   | 3.5 | RCU Analogies and Design Patterns                        |

|   | 3.6 | Discussion                                               |

|   | _   | , and DOU                                                |

| 4 | _   | olementing RCU                                           |

|   | 4.1 | RCU API                                                  |

|   |     | 4.1.1 Read-Side RCU API                                  |

|   |     | 4.1.2 Write-Side RCU API                                 |

|   | 4.0 | 4.1.3 List-Manipulation RCU API                          |

|   | 4.2 | Implementing Grace-Period Detection                      |

|   | 4.3 | Inducing Quiescent States                                |

|   |     | 4.3.1 Simple Induced Quiescent States                    |

|   |     | 4.3.2 Induced Quiescent States With Batching (batch) 111 |

|   | 4.4  | Observ  | ving Naturally Occurring Quiescent States |

|---|------|---------|-------------------------------------------|

|   |      | 4.4.1   | Counters and Barrier (rcu-ltimer)         |

|   |      | 4.4.2   | Counter Ring (rcu-sched)                  |

|   |      | 4.4.3   | Token Ring with Preemption (K42)          |

|   | 4.5  | Single  | -CPU RCU Implementation                   |

|   | 4.6  | Discus  | sion                                      |

|   |      | 4.6.1   | RCU API Discussion                        |

|   |      | 4.6.2   | RCU Infrastructure Discussion             |

| 5 | Des  | ign Pa  | tterns for RCU                            |

| • | 5.1  | •       | ple Algorithm                             |

|   | 5.2  | _       | Design Patterns                           |

|   | 0.2  | 5.2.1   | Forces                                    |

|   |      | 5.2.2   | Non-RCU Locking Design Patterns           |

|   |      | 5.2.3   | Pure RCU                                  |

|   |      | 5.2.4   | RCU Existence Locks                       |

|   |      | 5.2.5   | Reader-Writer-Lock/RCU Analogy            |

|   |      | 5.2.6   | RCU Readers With NBS Writers              |

|   | 5.3  | Patter  | rns for Transforming Algorithms to RCU    |

|   |      | 5.3.1   | Forces                                    |

|   |      | 5.3.2   | Mark Obsolete Objects                     |

|   |      | 5.3.3   | Substitute Copy For Original              |

|   |      | 5.3.4   | Impose Level Of Indirection               |

|   |      | 5.3.5   | Ordered Update With Ordered Read          |

|   |      | 5.3.6   | Global Version Number                     |

|   |      | 5.3.7   | Stall Updates                             |

|   | 5.4  | Discus  | ssion                                     |

|   |      | 5.4.1   | Index to Locking Design Patterns          |

|   |      | 5.4.2   | Index to Transformational Patterns        |

| 6 | Solo | octed A | Applications of RCU Design Patterns       |

| U | 6.1  |         | n V IPC                                   |

|   | 0.1  | 6.1.1   | Semaphore Data Structures                 |

|   |      | 6.1.1   | Semaphore Removal                         |

|   |      | 6.1.2   | Semaphore Lock Acquisition                |

|   |      | 6.1.4   | Semaphore Deferred Deletion               |

|   |      | 6.1.5   | Semaphore Array Expansion                 |

|   |      | 616     | Semaphore Operation 191                   |

|   |      |         |                                           |

|   |            | 6.1.7 Semaphore Discussion                              |

|---|------------|---------------------------------------------------------|

|   | 6.2        | Linux Directory-Entry Cache                             |

|   |            | 6.2.1 Visual Overview of dcache                         |

|   |            | 6.2.2 Applying RCU to dcache                            |

|   |            | 6.2.3 dcache Discussion                                 |

|   | 6.3        | RCU Synchronizing With NMIs                             |

|   | 6.4        | RCU and Module Race Reduction                           |

|   | 6.5        | Incremental Use of RCU on tasklist Locking              |

|   | 6.6        | Scalable FD Management                                  |

|   | 6.7        | K42 Hash Tables                                         |

|   | 6.8        | Other RCU Usage                                         |

|   |            | 6.8.1 VM/XA                                             |

|   |            | 6.8.2 DYNIX/ptx                                         |

|   |            | 6.8.3 RCU Use in K42                                    |

|   |            | 6.8.4 RCU Use in Linux                                  |

|   | 6.9        | Discussion                                              |

| 7 | Ans        | alytical Comparison of RCU and Locking                  |

| • | 7.1        | Low-Contention Analytic Methodology                     |

|   | •          | 7.1.1 Memory-Latency Model                              |

|   |            | 7.1.2 Conditions and Assumptions                        |

|   |            | 7.1.3 Procedural Details                                |

|   | 7.2        | Low-Contention Derivations                              |

|   |            | 7.2.1 Derivation for Spinlock                           |

|   |            | 7.2.2 Derivation for Distributed Reader-Writer Spinlock |

|   |            | 7.2.3 Derivation for RCU                                |

|   |            | 7.2.4 Comparison                                        |

|   | 7.3        | Discussion                                              |

| 8 | Mes        | asured Comparison of RCU and Locking                    |

|   | 8.1        | Comparison to Locking                                   |

|   | 8.2        | Comparison to Analytic Results                          |

|   | 8.3        | Evaluation of Techniques for Identifying Grace Periods  |

|   | 0.0        | 8.3.1 RCU Complexity                                    |

|   |            | 8.3.2 RCU Overhead When Idle                            |

|   |            | 8.3.3 Grace-Period Latency                              |

|   |            | 8.3.4 RCU Overhead When In Use                          |

|   | <b>Q</b> / | Discussion and Future Scenarios                         |

|    |         | 8.4.1         | Uniprocessor Über Alles                                               |

|----|---------|---------------|-----------------------------------------------------------------------|

|    |         | 8.4.2         | Multithreaded Mania                                                   |

|    |         | 8.4.3         | More of the Same                                                      |

|    |         | 8.4.4         | Crash Dummies Slamming into the Memory Wall                           |

|    |         | 8.4.5         | Discussion of Future Scenarios                                        |

| 9  | Con     | clusio        | ns and Future Work                                                    |

|    | 9.1     | Summ          | ary and Conclusions                                                   |

|    |         | 9.1.1         | Challenges to Traditional Synchronization Mechanisms 290              |

|    |         | 9.1.2         | Definition of RCU                                                     |

|    |         | 9.1.3         | Relation of RCU to Traditional Synchronization Mechanisms $\dots 292$ |

|    |         | 9.1.4         | Analytic and Empirical Performance Evaluation                         |

|    |         | 9.1.5         | Generality of RCU Via Design Patterns                                 |

|    |         | 9.1.6         | RCU Has Practical Value                                               |

|    |         | 9.1.7         | Summary                                                               |

|    | 9.2     | Future        | e Work                                                                |

|    |         | 9.2.1         | RCU Infrastructure                                                    |

|    |         | 9.2.2         | RCU Design Patterns                                                   |

|    |         | 9.2.3         | RCU and Non-Blocking Synchronization                                  |

|    |         | 9.2.4         | RCU Uses in the Linux Kernel                                          |

|    |         | 9.2.5         | Suitability of RCU to Other Environments                              |

|    |         | 9.2.6         | RCU Performance                                                       |

|    |         | 9.2.7         | RCU Semantics                                                         |

|    | 9.3     | Conclu        | iding Remarks                                                         |

| Bi | bliog   | graphy        |                                                                       |

| A  | Hist    | torical       | SMMP CPU Performance                                                  |

| В  | Meı     | mory (        | Ordering Issues                                                       |

|    |         |               |                                                                       |

| U  |         |               | l RCU Implementations                                                 |

|    | C.1     |               | ed Quiescent States With Batching (rcu-taskq)                         |

|    | C.2     |               | er Leveraging of Quiescent States                                     |

|    |         | C.2.1 $C.2.2$ | rcu-krcud                                                             |

|    |         | C.2.2         | X-rcu                                                                 |

|    | $C_{2}$ |               | rcu-poll                                                              |

|    | C.3     | r reem        | ption in Linux RCU (rcu-preempt)                                      |

| D RCU Performance on Large Hash Tables | <br> |  | <br>٠ |  | . 346 |

|----------------------------------------|------|--|-------|--|-------|

| Biographical Note                      | <br> |  |       |  | . 350 |

# List of Tables

| 2.1 | 700 MHz P-III Operation Costs                                                |

|-----|------------------------------------------------------------------------------|

| 2.2 | Attributes of Synchronization Mechanism                                      |

| 3.1 | Reader-Writer Locking and RCU                                                |

| 3.2 | Attributes of Deferred Destruction Mechanisms                                |

| 4.1 | RCU Implementations Inducing Quiescent States                                |

| 4.2 | RCU Implementations Observing Quiescent States                               |

| 5.1 | Reader-Writer-Lock/RCU Substitutions                                         |

| 5.2 | Locking Design Pattern Force Index                                           |

| 5.3 | RCU Transformational Pattern Index                                           |

| 6.1 | RCU Usage in Linux 2.6.0-test1                                               |

| 6.2 | DBT1 Database Benchmark Results (TPS)                                        |

| 6.3 | semopbench Microbenchmark Results (seconds)                                  |

| 6.4 | Semaphore Change in Lines of Code                                            |

| 6.5 | Applying RCU to get_pid_list()                                               |

| 6.6 | Applying RCU to get_pid_list() Helper Macros                                 |

| 7.1 | Nomenclature for Lock Cost Derivation                                        |

| 7.2 | Simple Spinlock Access-Type Probabilities and Latencies                      |

| 7.3 | Distributed Reader-Writer Spinlock Memory Layout                             |

| 7.4 | Unnormalized Probability Matrix for Distributed Reader-Writer Spinlock . 244 |

| 7.5 | Trace Labels                                                                 |

| 8.1 | RCU Implementation Complexity                                                |

| 8.2 | RCU Idle Overhead                                                            |

| 8.3 | dcachebench Comparison                                                       |

| A 1 | Historical SMMP CPU Performance 321                                          |

# List of Figures

| 1.1  | SMMP Efficiency for Sequent Computers                          | 2  |

|------|----------------------------------------------------------------|----|

| 2.1  | Instructions per Local Memory Reference for Sequent Computers  | 20 |

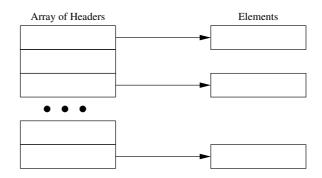

| 2.2  | Example Hash Table                                             | 21 |

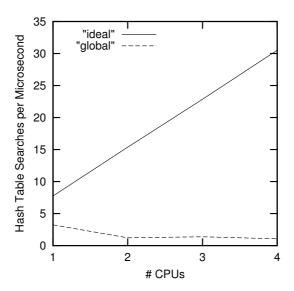

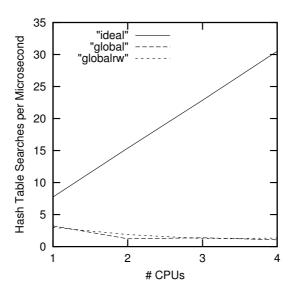

| 2.3  | Globally Locked Read-Only Hash Table Performance               | 23 |

| 2.4  | Globally Reader-Writer Locked Read-Only Hash Table Performance | 24 |

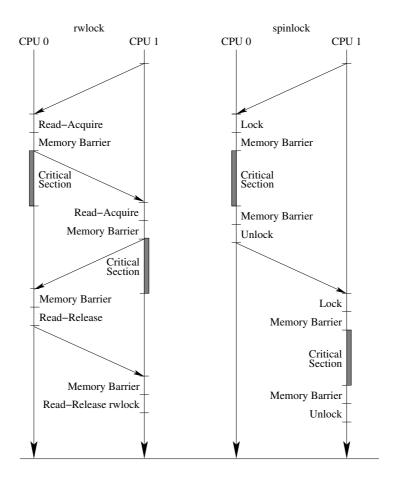

| 2.5  | Comparing rwlock and spinlock                                  | 26 |

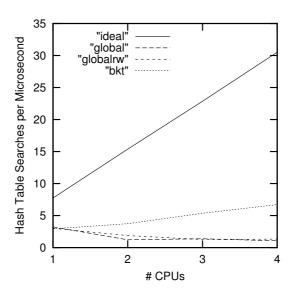

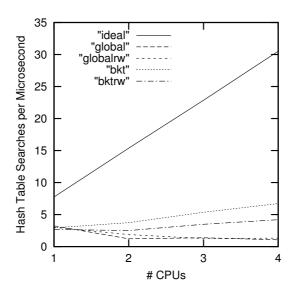

| 2.6  | Bucket-Locked Read-Only Hash Table Performance                 | 27 |

| 2.7  | Bucket-Reader-Writer-Locked Read-Only Hash Table Performance   | 28 |

| 2.8  | brlock Read-Only Hash Table Performance                        | 29 |

| 2.9  | Locked Increment                                               | 30 |

| 2.10 | Out of Order Locked Increment                                  | 30 |

| 2.11 | Locked Increment With Memory Barriers                          | 31 |

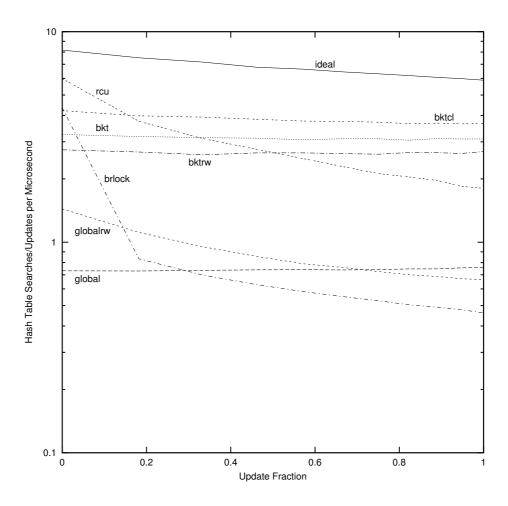

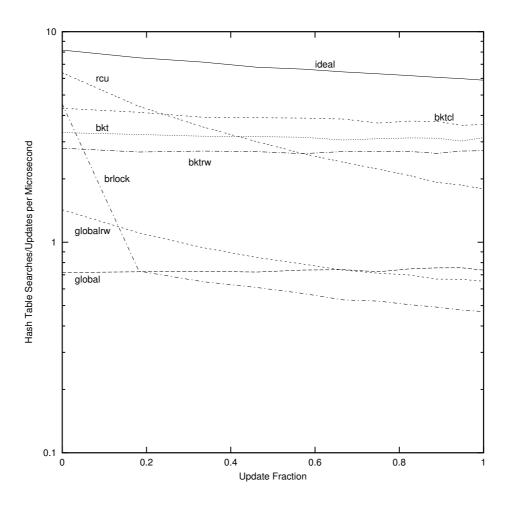

| 2.12 | Hash Table Performance for Mixed Workload on Four CPUs         | 34 |

| 2.13 | Hash Table Performance for Co-Located Lock                     | 37 |

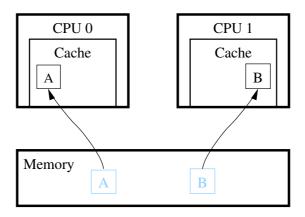

| 2.14 | Split Counter Initial Cache Configuration                      | 43 |

| 2.15 | Split Counter First Increment                                  | 43 |

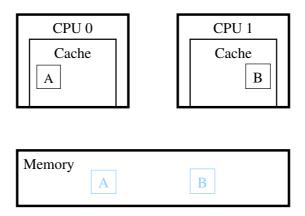

| 2.16 | Split Counter Subsequent Increments                            | 44 |

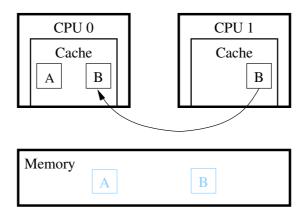

| 2.17 | Split Counter Readout                                          | 44 |

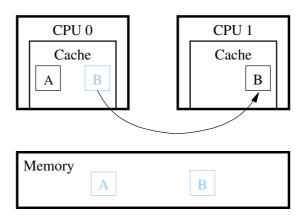

| 2.18 | Split Counter Increment After Readout                          | 45 |

| 2.19 | NBS Update: Conceptual View                                    | 48 |

| 2.20 | Non-Blocking Push                                              | 49 |

| 2.21 | Non-Blocking Pop                                               | 50 |

| 2.22 | Atomic Insertion Into a Linked List                            | 58 |

| 2.23 | Atomic Removal From a Linked List                              | 59 |

| 2.24 | Atomic Deletion From a Linked List                             | 60 |

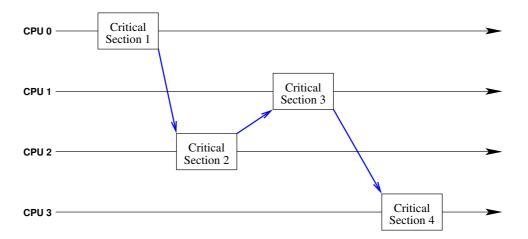

| 3.1  | Causal Ordering for Exclusive Locking                          | 75 |

| 3.2  | Causal Ordering for Reader-Writer Locking                      | 75 |

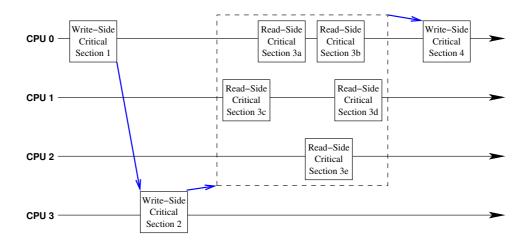

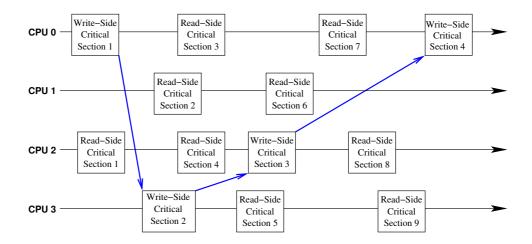

| 3.3  | Causal Ordering for RCU                                        | 76 |

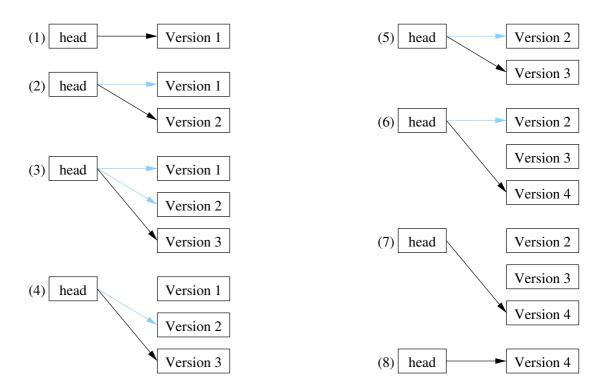

| 3 4  | RCII Multiple Version Handling                                 | 77 |

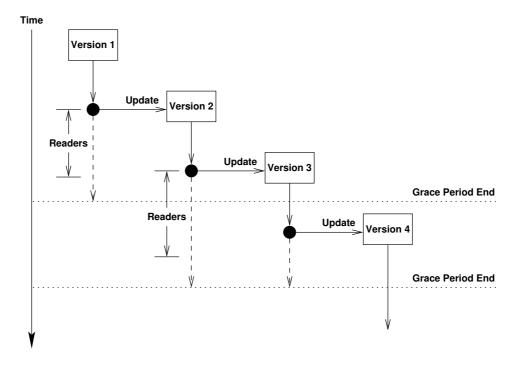

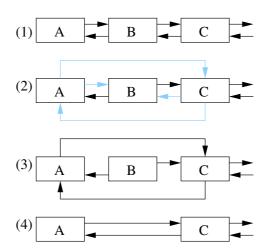

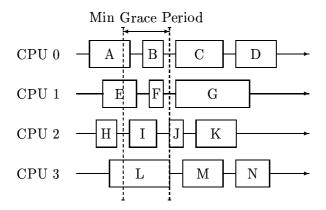

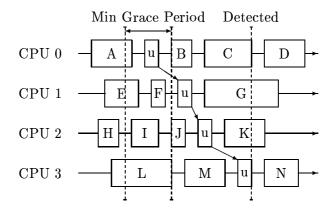

| 3.5  | RCU Multiple Version Timeline                                  |

|------|----------------------------------------------------------------|

| 3.6  | RCU Concepts                                                   |

| 3.7  | Search-List Data Structures                                    |

| 3.8  | Internal Search Algorithm                                      |

| 3.9  | RCU Destruction Determination                                  |

| 4.1  | RCU API                                                        |

| 4.2  | RCU List API                                                   |

| 4.3  | Example Read-Side RCU Critical Section                         |

| 4.4  | Example Blocking Write-Side RCU Critical Section               |

| 4.5  | Example Non-Blocking Write-Side RCU Critical Section           |

| 4.6  | Example Read-Side Use of RCU List-Manipulation Primitives 107  |

| 4.7  | Example Write-Side Use of RCU List-Manipulation Primitives 108 |

| 4.8  | RCU Grace Period                                               |

| 4.9  | Simple Grace-Period Detection                                  |

| 4.10 | Non-Preemptible Grace-Period Detection                         |

| 4.11 | Non-Blocking Grace-Period Detection                            |

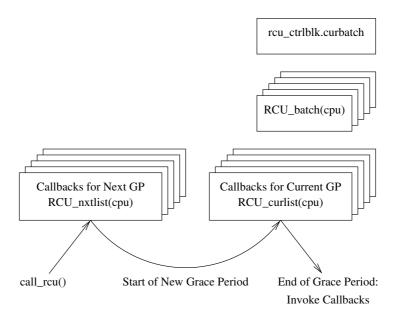

| 4.12 | RCU Callback Tracking (rcu-ltimer)                             |

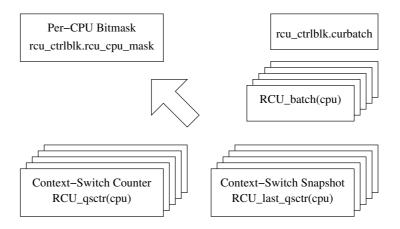

| 4.13 | rcu-ltimer Barrier-Computation Variables                       |

| 4.14 | rcu-ltimer call_rcu() Implementation                           |

| 4.15 | rcu-ltimer Scheduler Instrumentation                           |

| 4.16 | rcu-ltimer Per-CPU Timer Instrumentation                       |

| 4.17 | rcu-ltimer RCU-Callback-Pending Check                          |

| 4.18 | rcu-ltimer Tasklet Scheduling                                  |

| 4.19 | rcu-ltimer Callback Advancement                                |

| 4.20 | rcu-ltimer Callback Invocation                                 |

| 4.21 | rcu-ltimer Starting New Grace Period                           |

| 4.22 | rcu-ltimer Check for Quiescent State                           |

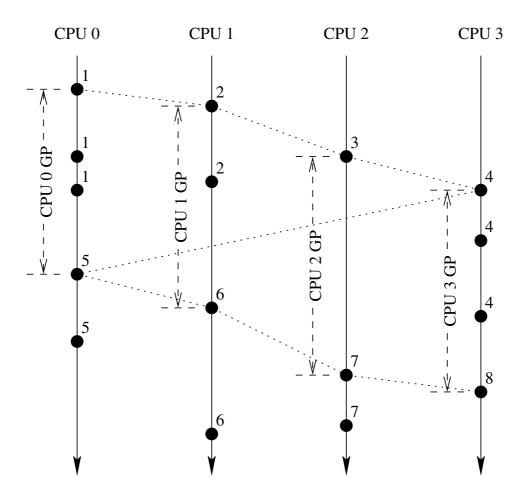

| 4.23 | Overlapping Grace Periods for Counter Ring                     |

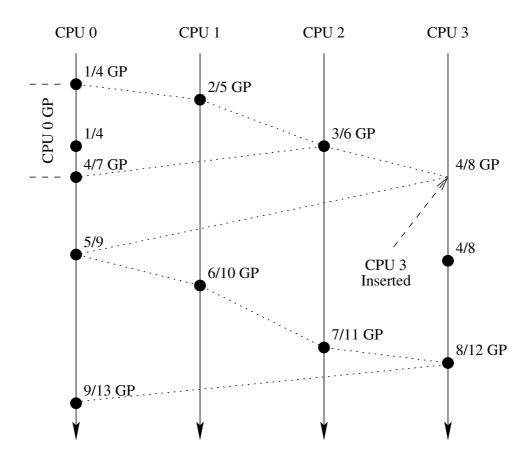

| 4.24 | Counter Ring and CPU Hotplug                                   |

| 4.25 | rcu-sched call_rcu() Implementation                            |

| 4.26 | rcu-sched Scheduler Instrumentation, Part 1                    |

| 4.27 | rcu-sched Scheduler Instrumentation, Part 2                    |

| 4.28 | rcu-sched Idle Loop Instrumentation                            |

| 4.29 | rcu-sched rcu_batch_done()                                     |

| 5.1  | Lookup-Table Element                                           |

| 5.2  | Lookup-Table Search                                            |

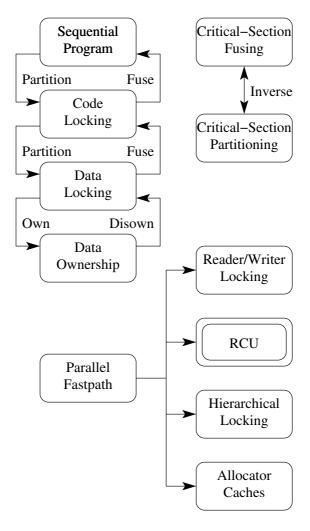

| 5.3  | Relationship Among Patternssss                   |

|------|--------------------------------------------------|

| 5.4  | RCU Existence Locks                              |

| 5.5  | RCU Read-Side Code                               |

| 5.6  | RCU Write-Side Locking                           |

| 5.7  | Mark Obsolete Object Reader                      |

| 5.8  | Mark Obsolete Object Search                      |

| 5.9  | Mark Object Obsolete Upon Deletion               |

| 5.10 | Substituting a Copy For Original                 |

| 5.11 | Substituting a Copy For Original Read            |

| 5.12 | Ordered Update With Ordered Read                 |

| 5.13 | Non-Blocking Global Version Number Update        |

| 5.14 | Stallable Update                                 |

| 5.15 | Stalling Updates                                 |

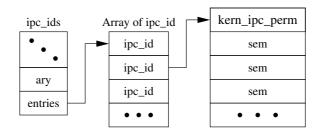

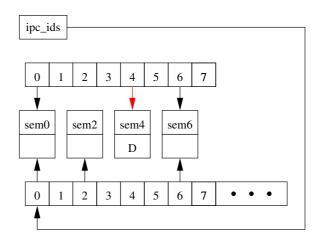

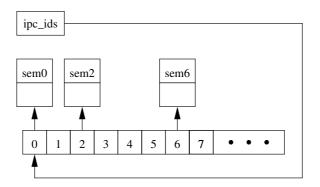

| 6.1  | Semaphore Structures with Global Locking         |

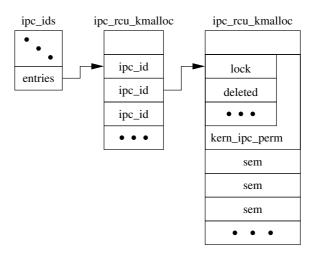

| 6.2  | Semaphore Structures with RCU                    |

| 6.3  | Semaphore Deletion                               |

| 6.4  | Detecting Semaphore Deletion                     |

| 6.5  | Freeing a Semaphore                              |

| 6.6  | Expanding the Array of Pointers to Semaphores    |

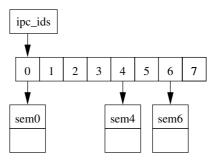

| 6.7  | Semaphore Initial State                          |

| 6.8  | Semaphore Structures After Array Replacement     |

| 6.9  | Semaphore Structures After Grace Period          |

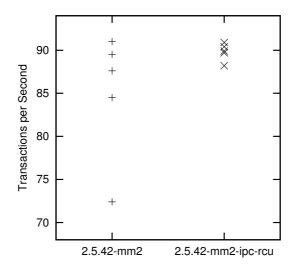

| 6.10 | DBT1 Database Benchmark Raw Results              |

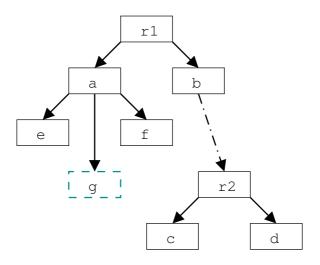

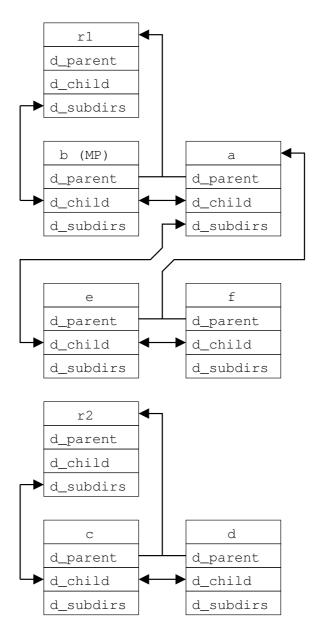

| 6.11 | Example Filesystem Tree                          |

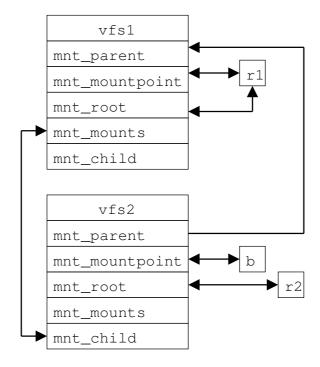

| 6.12 | dcache Representation of Example Filesystem Tree |

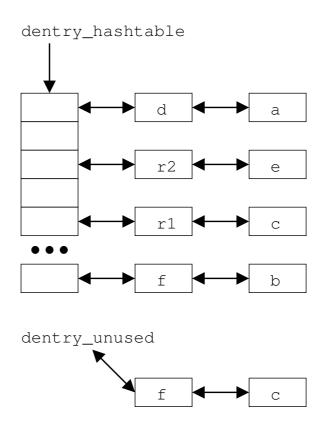

| 6.13 | dentry Hash Table                                |

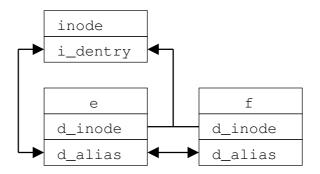

| 6.14 | Hard-Link Alias Chains                           |

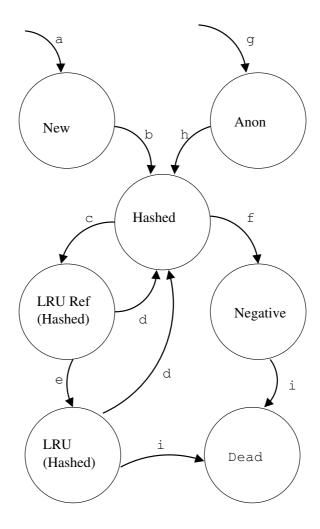

| 6.15 | dentry State Diagram                             |

| 6.16 | Traversing Mountpoints                           |

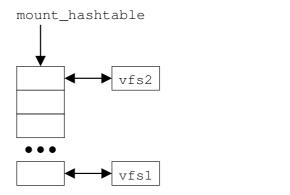

| 6.17 | VFS Mount Tree                                   |

| 6.18 | Lock-Free Pathname Segment Lookup                |

| 6.19 | Pathname Segment Lookup Rename Race Resolution   |

| 6.20 | Deferred Free of dentry Structures               |

| 6.21 | RCU Callback Function for dentries               |

| 6.22 | Renaming dentries                                |

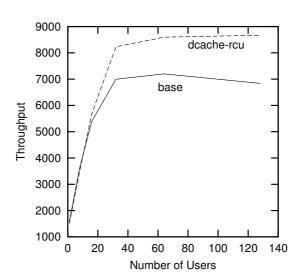

| 6 23 | Multiuser Benchmark Performance 210              |

| 6.24       | NMI Timer Stop Function                                             |

|------------|---------------------------------------------------------------------|

| 6.25       | oprofile Shutdown Code                                              |

| 6.26       | Module Unloading                                                    |

| 6.27       | Task-List RCU Patch                                                 |

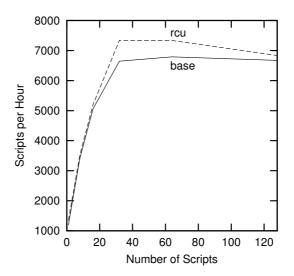

| 6.28       | SPEC SDET Performance of Task-List RCU                              |

| 6.29       | Expanding FD Array                                                  |

| 6.30       | RCU Expanding FD Array                                              |

| 6.31       | FD Management Performance                                           |

| 6.32       | Lock-Free Hash Remove Operation                                     |

| 6.33       | Lock-Free Hash Remove Operation with Race                           |

| 6.34       | PostMark Performance of Hash Table                                  |

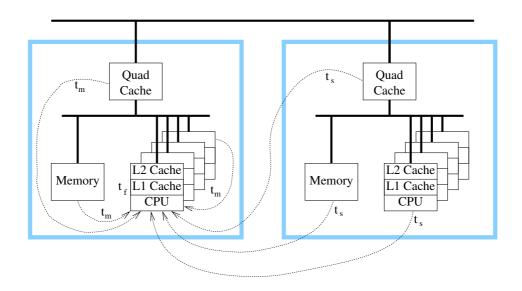

| 71         | NUMA Memory Latency                                                 |

| 7.1        | · ·                                                                 |

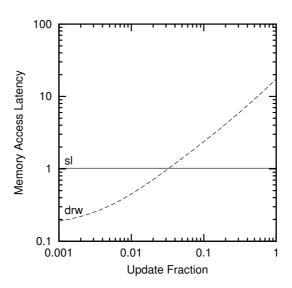

| 7.2        | Costs of Simple Spinlock and Distributed Reader-Writer Spinlock 249 |

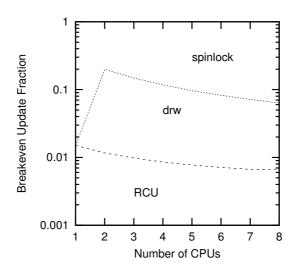

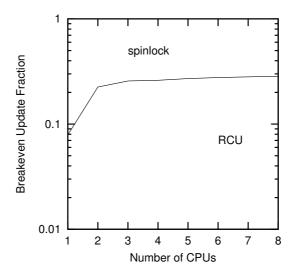

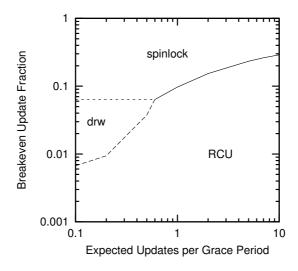

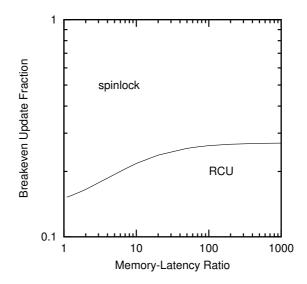

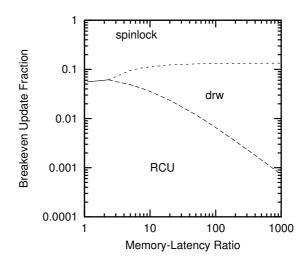

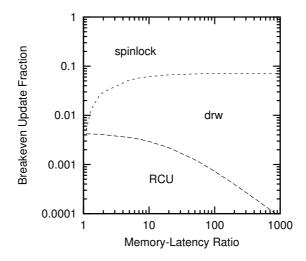

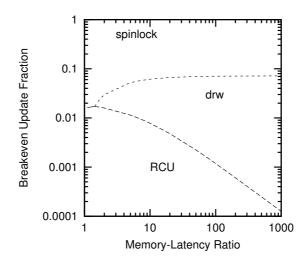

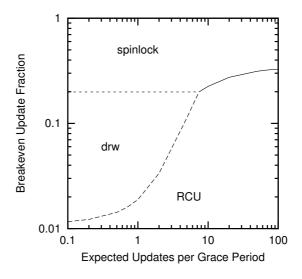

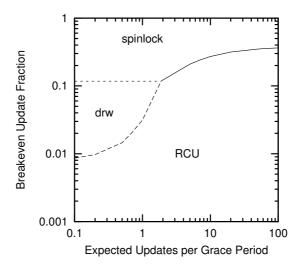

| 7.3        | Breakevens vs. Number of CPUs, $\lambda$ Small                      |

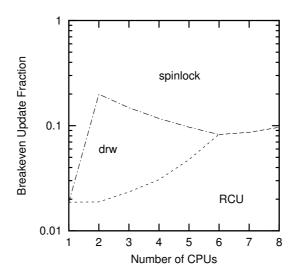

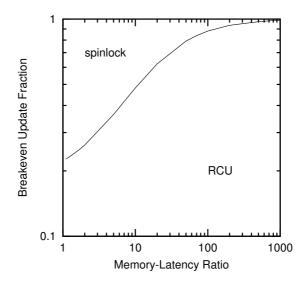

| 7.4        | Breakevens vs. Number of CPUs, $\lambda = 0.1$                      |

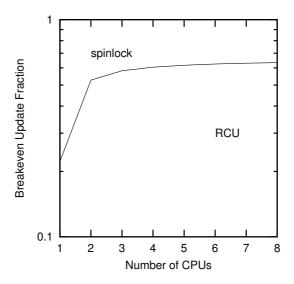

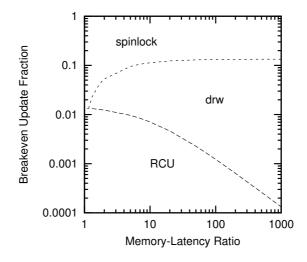

| 7.5        | Breakevens vs. Number of CPUs, $\lambda=1.0$                        |

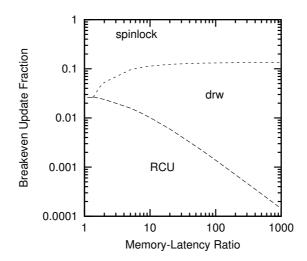

| 7.6<br>7.7 | Breakevens vs. Number of CPUs, $\lambda=10.0$                       |

|            | Breakevens vs. Number of CPUs, $\lambda$ Large                      |

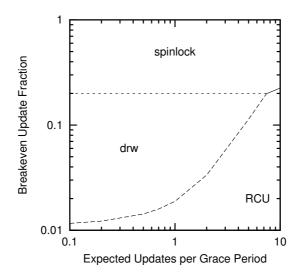

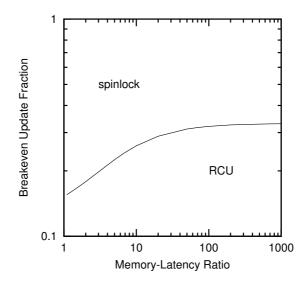

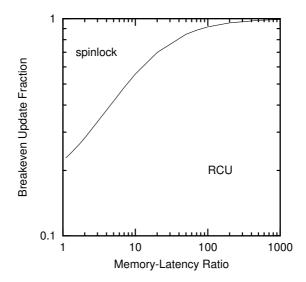

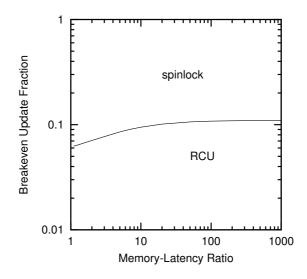

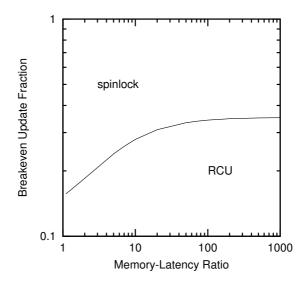

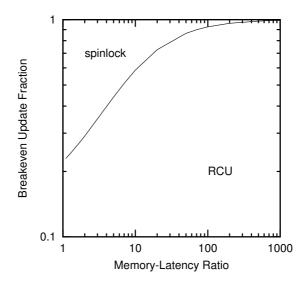

| 7.8        | Breakevens vs. $\lambda$ , Two CPUs                                 |

| 7.9        | Breakevens vs. $\lambda$ , Four CPUs                                |

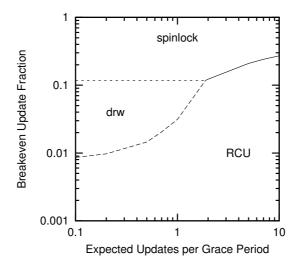

|            | Breakevens vs. $\lambda$ , Eight CPUs                               |

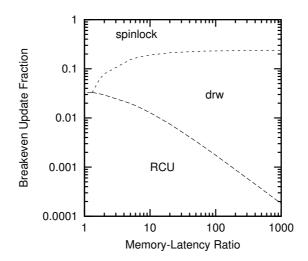

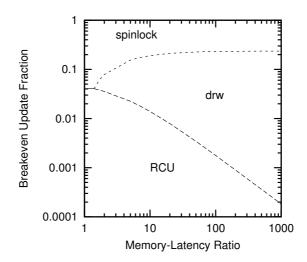

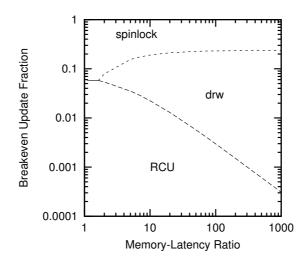

|            | Breakevens vs. $r$ , $\lambda$ Small, Two CPUs                      |

|            | Breakevens vs. $r$ , $\lambda$ =0.1, Two CPUs                       |

|            | Breakevens vs. $r$ , $\lambda=1.0$ , Two CPUs                       |

|            | Breakevens vs. $r$ , $\lambda = 10.0$ , Two CPUs                    |

|            | Breakevens vs. $r$ , $\lambda$ Small, Four CPUs                     |

|            | Breakevens vs. $r$ , $\lambda$ =0.1, Four CPUs                      |

|            |                                                                     |

|            | Breakevens vs. $r$ , $\lambda=1.0$ , Four CPUs                      |

|            | Breakevens vs. $r$ , $\lambda=10.0$ , Four CPUs                     |

|            | Breakevens vs. $r$ , $\lambda$ Small, Eight CPUs                    |

|            |                                                                     |

|            | Breakevens vs. $r$ , $\lambda$ =0.1, Eight CPUs                     |

|            | Breakevens vs. $r$ , $\lambda=1.0$ , Eight CPUs                     |

|            | Breakevens vs. $r$ , $\lambda$ Large Eight CPUs                     |

| 1.41       | - DIEGNEYCHA YA. J. A LIGIYE. 1718116 VI VA                         |

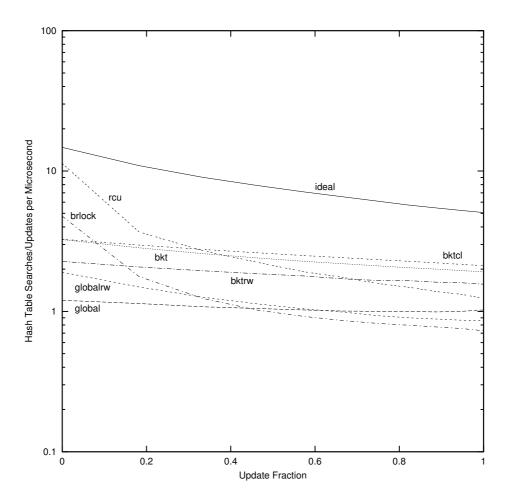

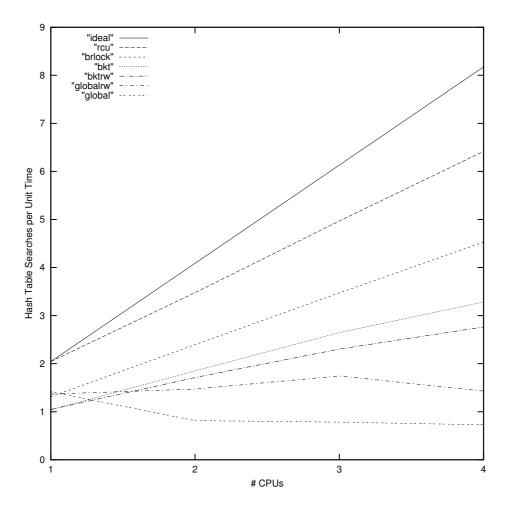

| 8.1  | Two-CPU Hash Table Performance for Short-Grace-Period Mixed Workload 27  | ′2         |

|------|--------------------------------------------------------------------------|------------|

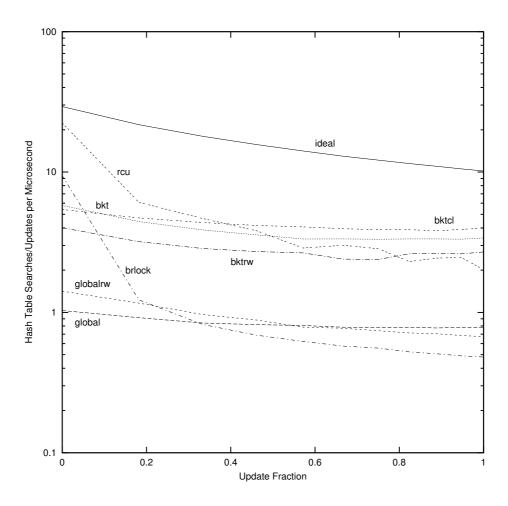

| 8.2  | Four-CPU Hash Table Performance for Short-Grace-Period Mixed Workload 27 | ′3         |

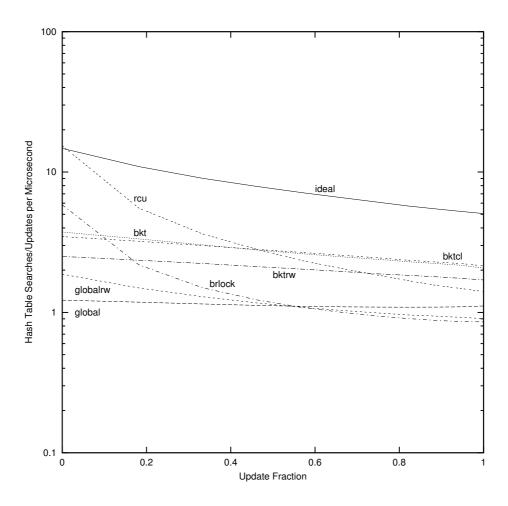

| 8.3  | Two-CPU Hash Table Performance for Long-Grace-Period Mixed Workload 27   | <b>'</b> 4 |

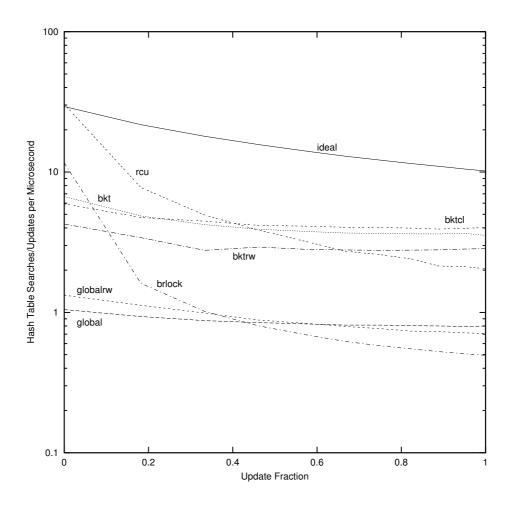

| 8.4  | Four-CPU Hash Table Performance for Long-Grace-Period Mixed Workload 27  | ′5         |

| 8.5  | RCU Hash Table Breakevens on Two CPUs                                    | <b>'</b> 6 |

| 8.6  | RCU Hash Table Breakevens on Four CPUs                                   | 7          |

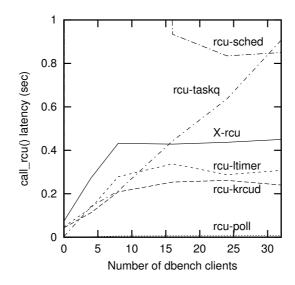

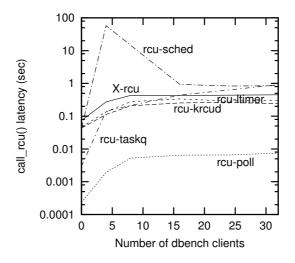

| 8.7  | call_rcu() Latency Under dbench Load                                     | 30         |

| 8.8  | call_rcu() Latency Under dbench Load (logscale)                          | 31         |

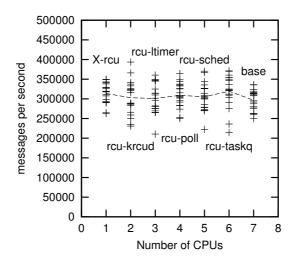

| 8.9  | RCU Performance on Chat Benchmark                                        | 3          |

| B.1  | Insert and Lock-Free Search                                              | 23         |

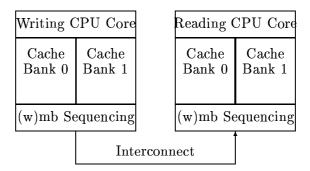

| B.2  | Why smp_read_barrier_depends() is Required                               | 24         |

| B.3  | Safe Insert and Lock-Free Search                                         | 25         |

| C.1  | rcu-taskq call_rcu() Implementation                                      | 27         |

| C.2  | rcu-taskq process_pending_rcus() Implementation                          | 28         |

| C.3  | rcu-taskq wait_for_rcu() Implementation                                  | 28         |

| C.4  | rcu-taskq krcud() Implementation                                         | 29         |

| C.5  | rcu-krcud call_rcu() Implementation                                      | 31         |

| C.6  | rcu-krcud Scheduler Instrumentation                                      | 31         |

| C.7  | rcu-krcud Timer Processing                                               | 31         |

| C.8  | $X$ -rcu call_rcu() Implementation                                       | 32         |

| C.9  | X-rcu Scheduler Instrumentation                                          | 3          |

| C.10 | X-rcu Timer Processing                                                   | 3          |

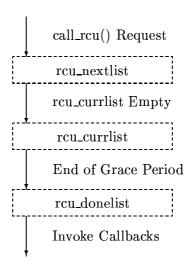

| C.11 | RCU Callback Flow                                                        | 34         |

| C.12 | $X$ - $rcu$ rcu_process_callbacks()                                      | 34         |

| C.13 | $X$ - $rcu$ rcu_move_next_batch()                                        | 35         |

| C.14 | $X$ -rcu rcu_check_quiescent_state()                                     | 37         |

| C.15 | $X$ - $rcu$ rcu_invoke_callbacks()                                       | 38         |

| C.16 | $X$ -rcu rcu_reg_batch()                                                 | 38         |

| C.17 | rcu-poll call_rcu() Implementation                                       | 39         |

| C.18 | rcu-poll Scheduler Instrumentation                                       | 39         |

| C.19 | rcu-poll Tasklet Body                                                    | 10         |

| C.20 | rcu-poll rcu_prepare_polling()                                           | Į1         |

| C.21 | rcu-poll rcu_polling()                                                   | Į1         |

| C.22 | rcu-poll rcu_completion()                                                | 12         |

|      | rcu-poll rcu_invoke_callbacks()                                          |            |

| C.24 | rcu_preempt Per-CPU Counters                                             | 15         |

| D.1 | Large Hash | Table | Performance         | for | Read-0 | Only ' | Work  | load |       |       |        | 347  |

|-----|------------|-------|---------------------|-----|--------|--------|-------|------|-------|-------|--------|------|

| D.2 | Large Hash | Table | ${\bf Performance}$ | for | Mixed  | Work   | kload | and  | Short | Grace | Period | 1348 |

| D.3 | Large Hash | Table | Performance         | for | Mixed  | Work   | kload | and  | Long  | Grace | Period | 349  |

# Abstract

**Exploiting Deferred Destruction:** An Analysis of Read-Copy-Update Techniques in Operating System Kernels

Paul E. McKenney

Supervising Professor: Jonathan Walpole

The Moore's-Law-driven performance of simple instructions has improved by orders of magnitude over the past two decades, but shared-memory multiprocessor (SMMP) synchronization operations have not kept pace. SMMP software uses synchronization operations heavily, thus suffering degraded performance and scalability. As a result, many traditional SMMP algorithms are now obsolete.

This dissertation presents read-copy update (RCU), a reader-writer synchronization mechanism in which read-side critical sections incur virtually zero synchronization overhead, thereby achieving near-ideal performance for read-mostly workloads. Write-side critical sections incur substantial synchronization overhead, deferring destruction and maintaining multiple versions of data structures in order to accommodate the synchronizationfree read-side critical sections. In addition, writers use some mechanism, such as locking, to ensure orderly updates.

Readers provide a signal enabling writers to determine when it is safe to complete destructive operations, but this signal may be deferred, permitting a single signal operation to serve multiple read-side RCU critical sections.

xxi

These read-side signals are observed by a specialized garbage collector, which carries out destructive operations once it is safe to do so. Garbage collectors are typically implemented in a manner similar to a barrier computation. Production-quality garbage collectors batch destructive operations, amortizing signal-observation overhead over many updates.

Although RCU is not itself new, its use has been quite specialized. This dissertation rectifies this situation by showing how RCU can be implemented efficiently in operating system kernels, by demonstrating its system-level performance and complexity benefits, and by providing a set of design patterns that make RCU more generally applicable.

This dissertation compares RCU to traditional synchronization mechanisms, including locking and non-blocking synchronization, using both analytic and empirical methods. The empirical methods include both informal micro-benchmarks and formal system-level benchmarks. These benchmarks show performance benefits ranging from tens of percent to an order of magnitude and little or no increase in code complexity.

Finally, this dissertation demonstrates that RCU has practical value by (1) outlining its use in several production systems, two of which have seen extensive datacenter use, one of which this author designed and implemented, and (2) documenting its widespread use in the Linux 2.6 kernel.

# Chapter 1

# Introduction

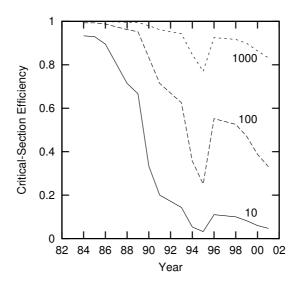

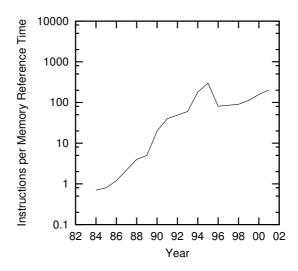

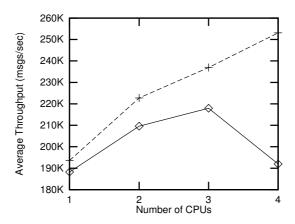

Although computer system performance has increased by several orders of magnitude over the past few decades, this Moore's-Law performance increase has not been so beneficial to shared-memory multiprocessor (SMMP) software, as shown by Figure 1.1. Each trace plots the ratio of the cost of the specified number of instructions to the cost of a spinlock-guarded critical section containing that same number of instructions, where contention is negligible and where both the lock and the data that it guards are contained in a single cache line. The instruction cost is estimated based on the published MIPS ratings for the older CPUs, and based on the clock frequency for newer CPUs. The cost of lock acquisition and release is estimated based on the cost of moving a line from one CPU's cache to another's. The raw data is displayed in Appendix A.1 on page 321.

This ratio is a measure of the efficiency of SMMP software for the specified critical-section size, measured in number of instructions. As can be seen in the figure, this efficiency has decreased precipitously since the early 1980s, so that SMMP algorithms that both performed and scaled extremely well two decades ago perform abysmally today. The Moore's-Law-induced changes in computer architecture have rendered such algorithms obsolete.

Since Moore's Law has brought huge benefits to computing and to society in general, it is only natural to ask why it has served SMMP software so poorly.

Figure 1.1: SMMP Efficiency for Sequent Computers

# 1.1 Where Has Moore's Law Gone Wrong?

The trend displayed in Figure 1.1 is nothing new, nor has it gone unnoticed [6, 17, 32, 38, 68, 73, 88, 117]. As discussed in these references, this trend has a number of underlying causes:

- 1. Electrical and speed-of-light effects have confined the sharpest rise in clock frequency to on-chip components. Connections between chips run at much lower clock frequencies, limiting bandwidths and degrading latencies for the chip-to-chip data paths connecting CPUs to each other and to memory.

- 2. Increasing memory size increases the depth of the address-decoding logic, thus increasing memory latency.

- 3. Increased memory latency is addressed by use of larger caches and larger numbers of levels of cache. Although these caches greatly improve average memory latency, they actually degrade worst-case latency, because each level in the hierarchy imposes a latency penalty, regardless of whether the access is satisfied from DRAM or from

another CPU's cache.

- 4. Some of the CPU core-clock frequency increase has been enabled by increasing the number of stages in CPU pipelines and by heuristic measures such as branch prediction. Although these longer pipelines increase best-case instruction rate, they also increase the penalty for branch mispredictions and other events that stall the pipeline. The increased penalty is due to the larger amount of partially executed instructions delayed or discarded when the longer pipeline is stalled.

- 5. Both increased memory latency and the overhead of pipeline stalls is partially addressed via superscalar CPUs, which do out-of-order and speculative execution. However, many SMMP algorithms do not tolerate such reordering, and they must therefore use special "memory barrier" instructions to enforce the needed ordering. Unfortunately, these memory-barrier instructions are quite expensive.

The result of these effects has been that although the single-threaded instruction-execution performance of CPUs has increased dramatically, the performance of CPU-to-CPU, CPU-to-memory, and pipeline-stall operations has not kept pace. However, these are extremely low-level micro-architectural issues. Have they really had significant impact on the performance of real-world software running on real-world computer systems?

## 1.2 SMMP Efficiency: The Effect on Real Code

The decrease in SMMP efficiency has been dramatic, as can be seen from Figure 1.1. In fact, Chapters 2, 7, and 8 will show that the performance of the synchronization operations traditionally used by SMMP software critically depends on the performance of CPU-to-CPU, CPU-to-memory and pipeline-stall operations that have been left in Moore's Law's wake.

In particular, Section 2.2 describes how traditional SMMP synchronization primitives rely on atomic instructions to update shared data. Because the data is shared, each such update will likely need to communicate with the CPU that performed the previous update, unless great care is invested into increasing temporal locality. The performance of such

CPU-to-CPU communication is quite slow, and is actually degraded by the same caches that are used to improve average memory-access latency. In addition, as noted earlier, most SMMP algorithms require that operations be ordered,<sup>1</sup> and the memory-barrier instructions used to accomplish this are quite expensive.

Recent hardware research has uncovered methods of optimizing the execution of critical sections, as is discussed in Section 2.2.15 on Page 55. However, all such hardware improvements are currently research prototypes, and will require some time to appear in commodity products, if in fact they ever do make their way into commodity products. Therefore, it makes sense to look for new ways of writing SMMP software so as to avoid these expensive operations.

#### 1.3 What Can Be Done?

Since the trends outlined in the previous sections are not new, one would expect that much work has already been done to address them. For example, one approach suggested directly by Figure 1.1 is simply to increase the size of critical sections, perhaps by merging adjacent sections. This approach has the benefit of decreasing complexity, but unfortunately typically also decreases scalability [66].

The opposite approach of partitioning critical sections across different data elements, or "data locking", has met with substantial success, as described in Section 2.2.7 on Page 25. However, even though data locking can greatly reduce lock contention, it does nothing to reduce the use of expensive atomic instructions and memory barriers.

In principle, read-mostly data structures can benefit from the greatly decreased levels contention provided by reader-writer locks, but, in practice, as will be shown in Section 2.2.6 on Page 23, memory latency often overwhelms the read-side parallelism benefits of reader-writer locking. Specialized asymmetric reader-writer locks can be used in some cases, but Section 2.2.9 on Page 28 will show how far short of ideal performance they fall, and Chapters 7 and 8 will demonstrate their shortcomings in update-intensive situations.

<sup>&</sup>lt;sup>1</sup>For example, it is not permissible to allow the operations following a lock acquisition to be executed before the lock acquisition completes. After all, the whole purpose of acquiring the lock is to protect those operations, and it cannot very well do so if they have been reordered to precede the lock acquisition.

Non-blocking synchronization (NBS) has seen much research activity over the past decade, and in fact Section 2.2.13 on Page 41 will show that simple forms of NBS have seen widespread use, though only in very specialized situations. Section 2.2.14 on Page 46 describes the difficulties that NBS has faced in more general situations, namely, that although it does eliminate lock contention, it introduces a similar form of contention-induced performance degradation due to repeated retries. In addition, NBS does nothing to reduce performance degradation due to the pipeline-stall and memory-latency overhead incurred by memory barriers and by atomic updates of shared memory. Nonetheless, many of the ideas put forth in NBS research are valuable in their own right, as will be shown in Chapter 5.

Section 2.2.16 on Page 56 will describe how the semantics of underlying data and operations may be exploited to increase performance and parallelism. In fact, the NBS split-counter example to be described in Section 2.2.13 on Page 2.2.13 exploits the commutative law of addition for exactly this purpose. However, these methods are specialized to specific situations, and thus are not generally applicable.

A number of researchers have noted that read-only accesses to read-mostly data structures may entirely dispense with synchronization operations if writers defer destruction [1, 30, 39, 53, 54, 56, 61, 62, 81, 86, 87, 91, 93]. Dispensing with synchronization operations in the read-only case is important: given that the concurrent readers need not communicate amongst themselves, the expensive synchronization operations are unnecessary, at least in principle. However, as will be discussed in Section 2.2.20 on Page 62, most of these researchers failed to present an efficient and robust mechanism for determining how long to defer destruction in SMMP environments lacking a garbage collector, but with long-running processes. Even those researchers who provided such a mechanism either:

- 1. imposed memory-barriers on readers, with attendant pipeline-stall overhead [86, 87];

- 2. implemented a solution that ran only on a single CPU architecture, and that was exploited only in an ad-hoc fashion [81, 108]; or

- 3. exploited their solution for only one of the many purposes to which it could profitably be put [30].

The fact that so much work has provided so little benefit for read-mostly SMMP situations raises the question of whether we need to return to basic principles in order to better understand exactly what benefit can be provided.

#### 1.4 Returning to Basic Principles

Section 2.3.2 on Page 65 will abstract three basic principles from the related work surveyed in Chapter 2:

- 1. Avoid expensive operations, namely those incurring pipeline-stall and memory-latency overheads.

- 2. Architect, design, and implement algorithms that permit fully parallel execution, thereby avoiding contention.

- 3. Architect, design, and implement algorithms that meet software-engineering needs, including simplicity, resilience against denial-of-service attacks, and tolerance for incremental adoption.

This dissertation will apply these principles to read-mostly data structures, such as those representing hardware and software configuration in operating-system kernels. Doing so results in significant performance improvements ranging from tens of percent to an order of magnitude with little or no increase in complexity. These benefits are obtained by refining the definition and use of a deferred-destruction technique, namely read-copy update, which will henceforth be abbreviated as RCU.

# 1.5 Description of RCU

RCU is a reader-writer synchronization mechanism that takes asymmetric distribution of synchronization overhead to its logical extreme: read-side critical sections incur zero

<sup>&</sup>lt;sup>2</sup>The name "read-copy update" originated from its ability to permit readers to run concurrently with updates, as long as the updates use copy operations so as to appear atomic to the readers. This idiom (or "design pattern") is described in more detail in Section 5.3.3 on Page 163.

synchronization overhead, containing no locks, no atomic instructions, and, on most architectures, no memory-barrier instructions. RCU therefore achieves near-ideal performance for read-only workloads on most architectures, and can greatly simplify the structure of some algorithms [30]. Write-side critical sections must therefore incur substantial synchronization overhead, deferring destruction and maintaining multiple versions of data structures in order to accommodate the read-side critical sections. In addition, writers must use some synchronization mechanism, such as locking, to handle concurrent updates.

Readers must provide a signal enabling writers to determine when it is safe to complete destructive operations, but this signal may be deferred, permitting a single signal operation to serve multiple read-side RCU critical sections. RCU typically signals writers by non-atomically incrementing a local counter, which is an extremely inexpensive operation.

These read-side signals are observed by a specialized distributed garbage collector, which uses a lazy barrier or a combining tree to sense the reader signals, and carries out destructive operations once all readers have signalled that it is safe to do so. Garbage collectors are typically implemented in a manner similar to a barrier computation, or, on NUMA systems, a combining tree. Production-quality garbage collectors batch destructive operations, so as to amortize their overhead over many write-side update operations.

RCU provides concurrent reads: because readers do not use any synchronization mechanism, there is no way for readers to avoid concurrency. For the same reason, RCU provides concurrent reads and writes. RCU does not specify whether writers may run concurrently with each other; write-side concurrency depends instead on the chosen write-side synchronization mechanism. The fact that RCU read-side critical sections use no synchronization mechanisms means that there is no overhead due to pipeline stalls, memory latency, contention, or locking for readers. Write-side overhead depends on the chosen write-side synchronization mechanism, but contention is reduced due to the fact that readers do not use any synchronization mechanisms.

In practice, it is also important that the read-side signalling occur reasonably frequently, since during a time interval in which a given CPU fails to provide such a signal, pending destructive operations cannot be carried out. If this condition persists, all available memory could be consumed tracking these pending destructive operations.

RCU is not new. The first mention of a similar mechanism occurred in 1980 [56], an early implementation was used in production in the late 1980s [39], and more efficient implementations followed in the 1990s [108, 81, 30]. Given RCU's long history, what research challenges could possibly remain?

#### 1.6 RCU Research Challenges

The first challenge is to identify the deficiencies of traditional synchronization mechanisms, for if there are no compelling deficiencies, then there is no reason to adopt a new synchronization mechanism. Chapter 2 takes up this task.

The second challenge is to articulate clearly the conceptual basis for RCU, showing how it operates and what form of synchronization it provides. This challenge is met by Chapter 3.

The third challenge is to provide an efficient and robust implementation of RCU that meets the simplicity and portability needs of general-purpose operating systems. The efficiency of the RCU implementation is critically important, because the write-side overhead of a wasteful implementation could overwhelm the read-side savings. A description of six candidate implementations for the Linux kernel, written by various Linux-community members, may be found in Chapter 4. One of these candidates was accepted into the Linux 2.6 kernel.

In its raw form, RCU is quite difficult to use because readers can see stale data as well as inconsistent views of non-atomically updated data. The use of RCU in its raw form is restricted to very specialized situations. The fourth challenge is therefore to make RCU easier to use and more generally applicable, which is a software engineering challenge. Chapter 5 attacks this problem by presenting design patterns showing how RCU may be used, along with a transformational design pattern language that transforms algorithms that are unable to tolerate RCU's staleness and inconsistency properties into forms that are able to tolerate these properties. Chapter 6 presents uses of these patterns taken from VM/XA, DYNIX/ptx, Tornado, K42, and the Linux 2.6 kernel.

The final challenge is evaluating the performance and complexity of RCU. This challenge is taken up using analytic techniques in Chapter 7 and using empirical techniques with mini-benchmarks in Chapter 8. Chapter 6, along with its presentation of design-pattern usage, includes empirical measurements of RCU performance using formal benchmarks and simple empirical measurements of RCU code complexity.

These five challenges by no means exhaust RCU's research possibilities; areas of future work are presented in Section 9.2 on Page 9.2.

#### 1.7 Contributions of this Dissertation

The contributions of this dissertation include:

- 1. A survey of performance-related changes in computer-system architecture and of the consequent challenges to the synchronization mechanisms traditionally used by software running on SMMP systems.

- 2. The definition of a solution, namely RCU, to a set of concurrency problems stemming from these changes and challenges.

- 3. A presentation of the relationship between RCU and traditional synchronization mechanisms.

- 4. A demonstration of the performance benefits, ranging from tens of percent to an order of magnitude, that RCU can provide with little or no increase in complexity. This demonstration uses analytic methods, informal micro-benchmarks, and formal system-level benchmarks.

- 5. A set of design patterns that permit RCU to be profitably applied to a wide range of synchronization problems, along with examples where these patterns have been used, both by myself and by others.

- 6. A demonstration of the practical value of RCU, as evidenced by its use in several production systems, one of whose RCU infrastructure this author designed and

implemented. This practical value is further evidenced by RCU's acceptance and widespread use within the Linux 2.6 kernel.

Chapter 2 discusses related work, evaluating this work on the basis of an in-depth treatment of synchronization's performance and complexity problems. Chapter 3 presents an overview of RCU, including a short glossary and description of concepts. Chapter 4 describes a number of algorithms that have been used to implement deferred destruction, one of which has been accepted into the Linux 2.6 kernel. Chapter 5 extends a locking-design pattern language [67] to incorporate RCU, and also presents an additional pattern language which transforms existing algorithms into a form more compatible with RCU. Chapter 6 describes how RCU has been used in various operating-system kernels, evaluates its performance, and shows what patterns were used in each case. Chapter 7 analytically compares the performance of RCU to that of various locking techniques and Chapter 8 uses empirical measurements to compare alternative implementations of RCU infrastructure as well as to compare the performance of RCU, both to that of various locking techniques and to that predicted by the analysis. Finally, Chapter 9 presents conclusions and areas for further study.

# Chapter 2

### Related Work

A thread may be thought of as part of a running program, but it is useful to define this term in a broad sense, so that it includes any executing entity such as a process, task, coroutine, interrupt handler, or signal handler. In a group of cooperating threads, the results of each individual thread's computation might either affect or be affected by those of the other threads.

One problem arising in concurrent systems of cooperating threads is that of providing orderly access and updates to data. This problem, called synchronization, has received a great deal of attention over the past several decades. CPU designers provided synchronization operations at least four decades ago, and researchers have published many shelves full of textbooks, journal articles, and conference papers on hardware and software synchronization mechanisms.

This chapter reviews the major areas of synchronization research and identifies some key gaps, which this dissertation addresses. This chapter first focuses on synchronization in uniprocessor systems in Section 2.1, and then on synchronization in multiprocessor systems in Section 2.2. Section 2.3 provides summary and discussion.

## 2.1 Synchronization in Uniprocessor Systems

Interrupt handlers and preemptive scheduling introduced the need for synchronization, even on uniprocessors, many decades ago.

Consider, for example, a system running a single user thread that repeatedly computes some values, then writes these values to disk. The simplest implementation would

compute a given set of values, initiate the I/O that writes these values to disk, wait until this I/O completes, then start computing the next set of values. The problem with this implementation is that the disk is idle while the CPU computes a given set of values, and the CPU is idle while that set of values is written to disk. Because disks are slow devices, with response times of milliseconds, literally millions of instructions are wasted by the CPU while waiting for disk I/O to complete.

The standard solution to this problem is overlapped I/O, where the CPU computes one set of values while the previous set of values is being written to disk. However, this solution requires that there be a way of determining when the previous I/O completes, so that the corresponding memory may be reused. This determination is typically made via an interrupt, which causes a predetermined interrupt handler to be invoked. This interrupt handler invocation may be thought of as an unsolicited function call that preempts the currently running thread, resuming it upon return. Such an interrupt handler could free the memory upon I/O completion, thus permitting its reuse.

However, this solution immediately presents another problem. What if the running thread was itself allocating or freeing memory at the time that the interrupt occurred? If the memory allocator's data structures are in an inconsistent state at the time of the interrupt, the interrupt handler's attempt to free memory could result in a system crash, or worse.<sup>1</sup>

One solution is for the thread to disable interrupts while allocating or freeing memory. The interrupt handler will therefore never be invoked while the memory allocator's data structures are in an inconsistent state, thereby ensuring the memory allocator's integrity. Disabling interrupts has been a standard technique for many decades; The 1965 CDC 3300 [20, 89] was capable of disabling interrupts, and it was not the first computer to do so. However, disabling interrupts introduces yet another problem, namely that it can delay invocation of the interrupt handler or result in an interrupt being "lost", so that a pair of consecutive interrupts results in the handler being invoked only once.

One the one hand, if delay is acceptable, then the standard technique is for the interrupt

What could possibly be worse than a system crash? Intermittent silent data corruption! Everything looks fine, but the answer is wrong. Sometimes. For no apparent reason.

handler to check the device state before returning, thus handling any number of interrupts that might have been lost. On the other hand, if delay is unacceptable, another well-known solution is for the thread and the interrupt handler to use atomic instructions to manipulate shared data structures. This use of atomic instructions, such as the CDC 3300's "Replacement Add" or the x86 locked exchange instructions [51], result in all manipulations of the memory allocator's data structure being atomic, so that the interrupt handler always sees this data structure in a consistent state. However, this approach solves the problem efficiently only for data structures amenable to atomic manipulation.

Operating-system and device-driver writers have used interrupt disabling as a synchronization mechanism for many years. However, this mechanism must be used carefully to avoid interfering with critical system services, such as thread scheduling and network protocol handling, that depend on timer interrupts. For this reason, untrusted user threads cannot be allowed to disable interrupts.

#### **Suppressing Preemption**

An alternative approach is to provide synchronization primitives to user threads. One way to accomplish this is to provide a system call that sets a bit in the kernel that prevents the scheduler from preempting the currently running thread. All I/O and timer interrupt handlers would then run normally, permitting the kernel to properly interact with I/O hardware and networking protocols, while still preventing any other user threads from accessing data that the currently running thread has left in an inconsistent state. This approach still permits a malicious or buggy user thread to disable preemption for extended time periods. However, the operating system can periodically regain control and kill an offending thread.

Given a preemption-suppressing system call, a typical method of safely incrementing a variable is as follows:

- 1. Suppress preemption.

- 2. Load the variable into a register.

- 3. Increment the register.

- 4. Store the register into the variable.

- 5. Enable preemption.

Once a given thread executes step 1 of this procedure, no other threads may run. The three-step increment of the variable thus appears atomic to these other threads, as required. Step 5 then re-enables preemption, permitting other threads to run. If all threads use the above procedure, the variable will be atomically incremented, so that no increments are lost.

Although unconditional suppression of preemption is very simple, easy to use, and efficient, it can also be used in a denial-of-service attack, where a malicious thread disables preemption and then enters an infinite loop. As noted earlier, such attacks could be addressed by terminating threads that suppress preemption for too long, but repeated attacks could still consume much of the system's resources.

#### Uniprocessor Semaphores

One way to prevent such abuse is for the operating system to instead provide locking primitives to user threads. The prototypical example of such locking primitives are semaphores [25], which are implemented, for example, by the Unix System V semaphore primitive [139].

Although System V semaphores are quite flexible and feature-rich, they are frequently used as simple locks, for example to guard a Hoare monitor [47]. For sake of simplicity, this chapter will consider implementations of this subset of semaphore functionality.

To use a semaphore, one of the user threads would execute a semget() system call to allocate a semaphore. This semaphore is owned by the user running the set of cooperating threads, who can set permissions to prevent other users from interfering with the semaphore, thereby preventing denial-of-semaphore attacks.

Once a semaphore is created, threads with sufficient permissions may use the semop() system call to acquire and release the semaphore. If one thread holds the semaphore, other threads attempting to acquire it will block within the kernel until it has been released.

The kernel represents the semaphore with a data structure that includes: (1) an indication of whether the semaphore is available, and (2) a queue of threads waiting for the semaphore to become available. The operating-system kernel disables preemption if needed (for example, by disabling interrupts) while manipulating this data structure in order to maintain its integrity. This disabling of preemption is unconditional, which is acceptable because the kernel code base is trusted to restore preemption in a timely manner. Furthermore, in-kernel semaphore implementations need to disable preemption only while acquiring and releasing the semaphore, rather than for the full duration of the critical section.

The simplified version of the semaphore acquisition code might be implemented as follows in the kernel:

- 1. Disable interrupts (which has the side effect of disabling preemption).

- 2. While the semaphore is held by some other thread, repeat the following steps:

- (a) Add this thread to the tail of the queue of threads waiting for this semaphore.

- (b) Reenable interrupts.

- (c) Switch context to some other thread.

- (d) (Get here when the thread is awakened. It is not guaranteed that this thread will successfully acquire the semaphore, since some other thread may have acquired it between the time that the semaphore was released and the time that this thread started running.)

- (e) Disable interrupts.

- 3. Mark the semaphore as held by this thread.

- 4. Reenable interrupts.

Note that threads attempting to acquire the semaphore when it is already held will block, thereby returning control to the scheduler, which has the advantage of allowing the thread holding the semaphore to run, which hopefully allows that thread to release it in a timely fashion.

Releasing the semaphore would be implemented as follows:

- 1. Disable interrupts.

- 2. Mark the semaphore as released.

- 3. If the queue of threads waiting for this semaphore is nonempty:

- (a) Remove the first thread from the queue of threads waiting for this semaphore.

- (b) Awaken the newly removed thread.

- 4. Reenable interrupts.

Thus, the high-level semaphore synchronization mechanism is implemented in a layered fashion, in terms of a lower-level preemption-disabling mechanism. This means that semaphores may be implemented simply, efficiently, and safely on hardware with minimal synchronization features. All that is required is the ability to disable interrupts, which is available on all modern microprocessors.

# 2.2 Synchronization in SMMP Systems

The interrupt-disabling technique described in the previous section will fail on SMMP systems, since a pair of threads running on different CPUs could simultaneously acquire the semaphore. Both threads would believe that they held the semaphore, which could result in the application crashing, or, worse yet, silently corrupting the shared data. The approach of simply refusing to support SMMP systems is becoming less and less viable, given the advent of hardware multithreading in commodity microprocessors.

SMMP operating-system kernels clearly cannot rely solely on interrupt or preemption disabling; implementing the semaphore primitives on SMMP systems also requires some way of excluding other CPUs from a given critical section.

#### 2.2.1 Spinlocks

One approach is to use spinlock primitives to protect the semaphore. The difference between a spinlock and a semaphore is that a thread waiting to acquire a spinlock will busy-wait instead of blocking. Because spinlocks do not block, they do not need to interact with the scheduler, and can thus be implemented in terms of atomic instructions.

For example, the Linux kernel bases its spinlocks on the atomic decrement primitive. The spinlock is initialized to 1, and spinlock acquisition proceeds roughly as follows (the actual implementation is more complex for performance reasons):

- 1. Atomically decrement the spinlock value.

- 2. If the value was negative, someone else holds the spinlock, so busy-wait (or "spin") as follows:

- (a) If the spinlock value is now positive, restart the acquisition procedure from step 1.

- (b) Otherwise, restart the spin from step 2a.

If multiple CPUs simultaneously attempt to acquire the spinlock, the one that decrements the spinlock to zero will hold the spinlock, while the rest will spin in step 2 until the spinlock is released. The spinlock is released by setting its value back to 1.

Spinlocks may also be based on a number of other types of special instructions [26, 49], or even on normal loads and stores [24, 57], though this latter approach is quite complex and slow.

If a given CPU holds the spinlock for an extended period of time, the rest of the CPUs will waste a large amount of time in step 2 spinning for the spinlock. In such cases, it would be better to use a semaphore so that waiting threads could block, permitting other work to get done. In contrast, spinlocks are best for protecting short critical sections, where the duration of the critical section is shorter than twice the time required for the scheduler to switch from one thread to another.

### 2.2.2 SMMP Semaphores

SMMP semaphores may be constructed using spinlocks. In this implementation, the semaphore data structure therefore contains a spinlock in addition to the semaphore-held

indicator and the thread-waiting queue. SMMP semaphore acquisition is quite similar to that of the uniprocessor case, with the interrupt disabling replaced by spinlock acquisition:

- 1. Acquire the semaphore's spinlock.

- 2. While the semaphore is already held, repeat the following steps:

- (a) Add this thread to the tail of the queue of threads waiting for this semaphore.

- (b) Release the semaphore's spinlock.

- (c) Switch context to some other thread.

- (d) (Get here when the thread is awakened. It is not guaranteed that this thread will successfully acquire the semaphore, since some other thread may have acquired it between the time that the semaphore was released and the time that this thread started running.)

- (e) Acquire the semaphore's spinlock.

- 3. Mark the semaphore as held.

- 4. Release the semaphore's spinlock.

Processes waiting on the semaphore block in step 2c, allowing the CPUs to run other threads in the meantime.

Similarly, releasing a semaphore closely resembles the uniprocessor case:

- 1. Acquire the semaphore's spinlock.

- 2. Mark the semaphore as released.

- 3. If the queue of threads waiting for this semaphore is nonempty:

- (a) Remove the first thread from the queue of threads waiting for this semaphore.

- (b) Awaken the newly removed thread.

- 4. Release the semaphore's spinlock.

The spinlock guarantees that only one CPU at a time may manipulate the semaphore data structure. This is another example of a layered implementation of a synchronization primitive: the semaphore implementation is layered on top of the simpler spinlock implementation.

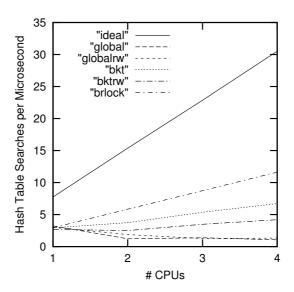

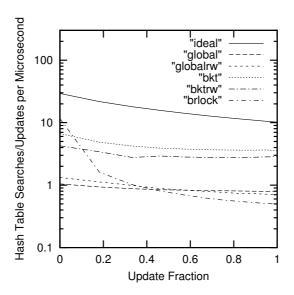

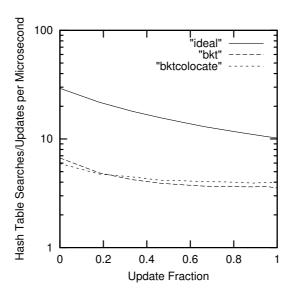

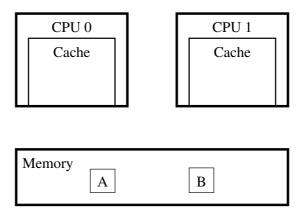

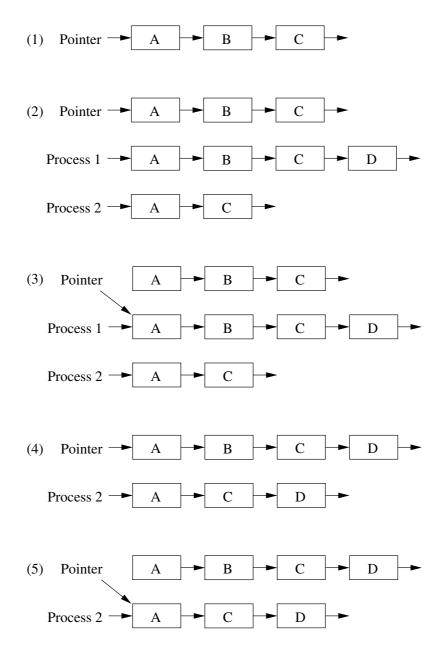

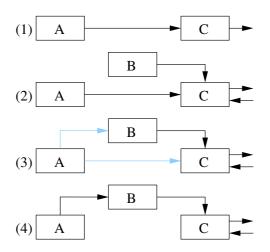

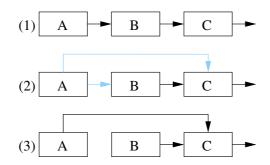

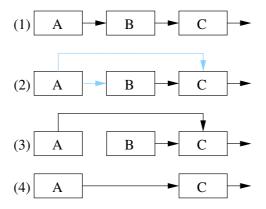

Both the spinlock and the semaphore provide the same function: mutual exclusion. However, there are performance differences. As noted earlier, spinlocks that are held for extended periods can result in the squandering of much CPU time spinning on the lock. On the other hand, semaphores inflict their own performance penalties in other situations. Because the semaphore acquires and releases a spinlock at least once during both semaphore acquisition and release, semaphores will be at least twice as expensive as spinlocks when there is no contention. Furthermore, the context-switch operation is itself relatively expensive. If only mild contention is expected, and if the critical sections take less time to execute than is required to do a context switch, it will be more efficient to spin than it will to context switch.